Le point de vue d’Intel sur la prochaine vague de la loi de Moore

La prochaine vague de la loi de Moore s’appuiera sur un concept en développement appelé co-optimisation de la technologie système, a déclaré Ann B.Kelleherdirecteur général du développement technologique chez Intel dans une interview avec Spectre IEEE avant son allocution plénière au Réunion IEEE sur les dispositifs électroniques 2022 (IEDM).

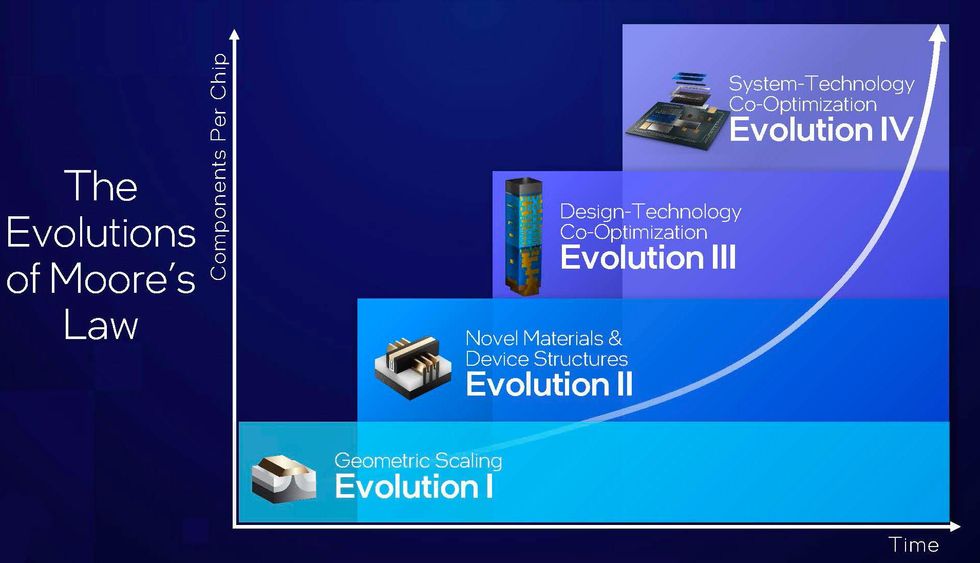

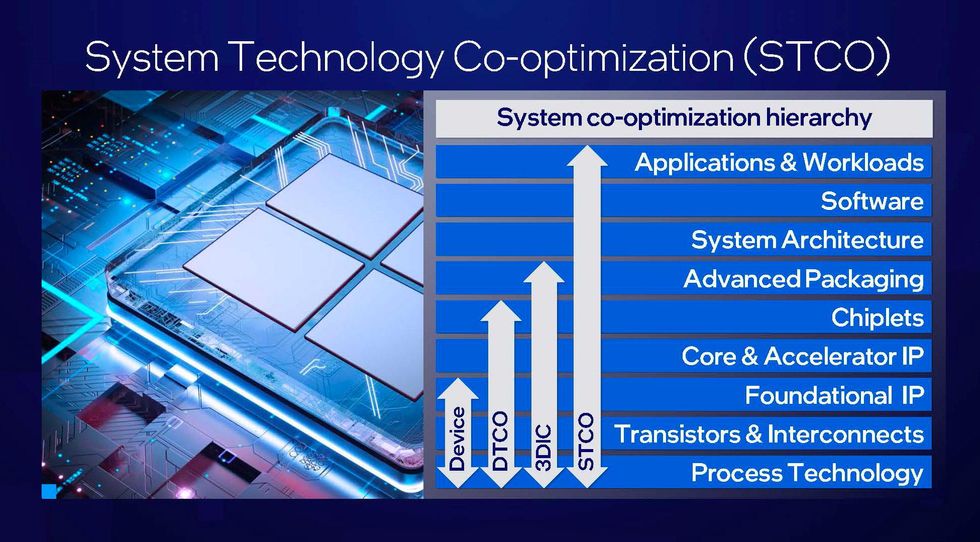

« La loi de Moore vise à accroître l’intégration des fonctions », explique Kelleher. “Alors que nous envisageons les 10 à 20 prochaines années, il y a un pipeline plein d’innovations” qui poursuivra la cadence des produits améliorés tous les deux ans. Cette voie comprend les améliorations continues habituelles des processus et de la conception des semi-conducteurs, mais la co-optimisation de la technologie système (STCO) fera la plus grande différence.

Kelleher l’appelle une manière de développement “de l’extérieur vers l’intérieur”. Cela commence par la charge de travail qu’un produit doit prendre en charge et son logiciel, puis descend jusqu’à l’architecture du système, puis quel type de silicium doit être dans un boîtier, et enfin jusqu’au processus de fabrication des semi-conducteurs. « Avec la co-optimisation de la technologie du système, cela signifie que toutes les pièces sont optimisées ensemble afin que vous obteniez la meilleure réponse pour le produit final », dit-elle.

STCO est désormais une option en grande partie parce que emballage avancé, tel que l’intégration 3Dpermet la connexion haut débit de chiplets—petites puces fonctionnelles—à l’intérieur d’un seul emballage. Cela signifie que ce qui serait autrefois des fonctions sur une seule puce peut être désagrégé sur des puces dédiées, qui peuvent ensuite être fabriquées en utilisant la technologie de traitement des semi-conducteurs la plus optimale. Par exemple, Kelleher souligne dans sa séance plénière que le calcul haute performance nécessite une grande quantité de mémoire cache par cœur de processeur, mais la capacité du fabricant de puces à réduire la SRAM ne progresse pas au même rythme que la réduction de la logique. Il est donc logique de créer des caches SRAM et des cœurs de calcul en tant que chiplets séparés en utilisant une technologie de processus différente, puis de les assembler à l’aide de l’intégration 3D.

Un exemple clé de STCO en action, dit Kelleher, est le Ponte Vecchio processeur au cœur du Aurore supercalculateur. Il est composé de 47 chiplets actifs (ainsi que de 8 blanks pour la conduction thermique). Ceux-ci sont cousus ensemble en utilisant à la fois des connexions horizontales avancées (technologie d’emballage 2.5D) et un empilement 3D. « Il rassemble du silicium de différentes usines et leur permet de se réunir afin que le système soit capable de fonctionner par rapport à la charge de travail pour laquelle il est conçu », dit-elle.

À l’IEDM, les ingénieurs d’Intel rapporteront qu’ils ont augmenté la densité de leur Technologie de collage hybride 3D dix fois par rapport à ce qu’ils ont rapporté en 2021. Une densité de connexion accrue signifie que davantage de fonctions de puce peuvent être désagrégées sur des puces séparées, offrant à leur tour plus de potentiel d’utilisation de STCO pour améliorer les résultats. Les pas de liaison hybrides, c’est-à-dire la distance entre les interconnexions, ne sont que de 3 micromètres avec cette nouvelle technologie. Avec cela, encore plus de cache peut être séparé des cœurs de processeur. Selon Kelleher, réduire le pas de liaison entre 2 micromètres et 100 nanomètres pourrait signifier être en mesure de commencer à séparer les fonctions logiques qui doivent aujourd’hui se trouver sur le même morceau de silicium.

La volonté d’optimiser les systèmes en désagrégeant les fonctions a des conséquences sur les futurs processus de fabrication des semi-conducteurs. La future technologie de traitement des semi-conducteurs doit faire face aux contraintes thermiques d’un environnement conditionné en 3D. Mais la technologie d’interconnexion verra probablement le plus grand changement. Kelleher dit qu’Intel est sur la bonne voie pour introduire une technologie qu’il appelle PowerVia (livraison de puissance à l’arrière, plus généralement) en 2024. PowerVia déplace le réseau d’alimentation d’une puce sous le silicium, réduisant ainsi la taille des cellules logiques et réduisant la consommation d’énergie. Mais cela « nous donne également différentes opportunités en termes de ce que nous pouvons et comment nous pouvons nous interconnecter dans le package », explique Kelleher.

Kelleher souligne que STCO en est encore à ses balbutiements. Les outils d’automatisation de la conception électronique (EDA) ont déjà abordé le prédécesseur de STCO, la co-optimisation de la technologie de conception (DTCO), qui se concentre sur les optimisations au niveau des cellules logiques et des blocs fonctionnels. “Mais certains des fournisseurs d’outils EDA travaillent déjà là-dessus”, dit-elle. “À l’avenir, l’accent sera mis sur les méthodes et les outils qui permettent d’activer STCO.”

Au fur et à mesure que STCO se développe, les ingénieurs d’appareils peuvent avoir à développer avec lui. “Généralement, les ingénieurs devront continuer à avoir leurs connaissances sur les appareils, mais aussi commencer à comprendre les cas d’utilisation de leur technologie et de leurs appareils”, explique Kelleher. “Plus de compétences interdisciplinaires seront nécessaires alors que nous nous dirigeons vers un monde plus STCO.”

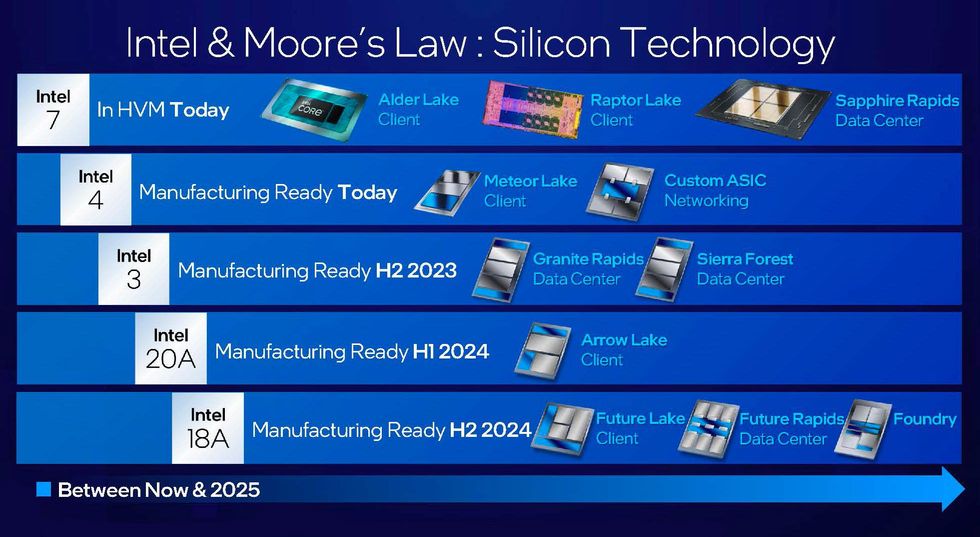

Feuille de route d’Intel

Kelleher a également mis à jour la feuille de route d’Intel, en la liant à la progression de la loi de Moore et à l’évolution de l’appareil depuis le invention du premier transistor. L’essentiel est que les choses sont sur la bonne voie depuis qu’Intel a annoncé son nouvelle feuille de route de fabrication il y a moins de deux ans, selon Kelleher. Mais elle a fourni quelques détails sur les processeurs qui feraient leurs débuts avec la nouvelle technologie.

L’Intel 20A, dont l’introduction en fabrication est prévue au premier semestre 2024, reste le grand saut technologique. Il introduit simultanément une nouvelle architecture de transistors -RibbonFET (plus généralement appelés transistors gate-all-around ou nanosheet) – et la fourniture d’alimentation par l’arrière PowerVia. Interrogé sur le risque encouru, Kelleher a expliqué la stratégie.

“Ils ne ont à faire immédiatement, mais nous voyons des avantages significatifs à passer à PowerVia pour permettre au [RibbonFET] technologie », dit-elle. Le développement se fait en parallèle pour réduire les risques de retards, explique-t-elle. Intel exécute un processus de test utilisant les FinFET, l’architecture de transistor utilisée aujourd’hui, avec PowerVia. « Cela a fonctionné avec beaucoup de succès et cela nous a permis d’accélérer notre travail de développement », dit-elle.

Le transistor du futur

Le discours de Kelleher intervient alors que L’IEEE Electron Device Society célèbre la 75e anniversaire de l’invention du transistor. À Spectre IEEEnous avons demandé à des experts à quoi pourrait ressembler le transistor à son 100e anniversaire en 2047. L’avis de Kelleher a pris en compte les longues durées de vie de la technologie des transistors, notant que la conception du transistor planaire a duré de 1960 à environ 2010, et que son successeur, le FinFET, est toujours aussi fort. “Maintenant, nous allons au RibbonFET qui va durer probablement encore plus de 20 ans… donc je pense que nous allons être quelque part avec des RibbonFET empilés”, a-t-elle suggéré. [Intel engineers describe that technology in the December 2022 issue of IEEE Spectrum.] Cependant, à ce moment-là, les rubans peuvent être constitués de semi-conducteurs 2D au lieu de silicium.

À partir des articles de votre site

Articles connexes sur le Web